CDプレイヤーのジッタが音質に影響すると言われています。 それを確かめるため、DAIFからのジッタをキャンセルする回路を作成しました。

DAIFからのデータをFIFOバッファに格納し、基板上に搭載したオシレータで読み出すことで、このオシレータのジッタのみが問題になる(はず)です。

1600×1200pixelの回路図はこちら。 電源、パスコンは記載していません。

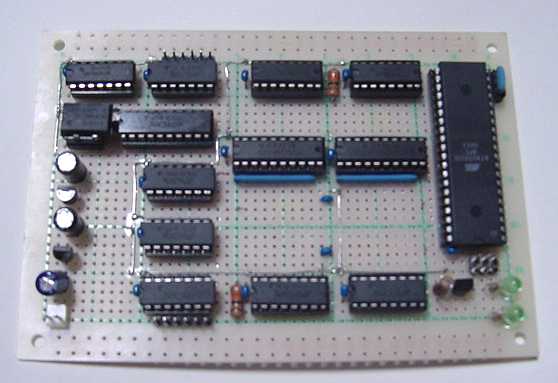

DAIからのBCK、LRCK、DATAをHC14で受け、HC595でパラレルに変換します。 HC595のラッチタイミングは、LRCKの変化点でパルスとなる信号をHC86で生成します。 行儀が悪いですが、フリップフロップが1個増えてしまうので手抜きをしています。

このパラレルデータを、SRAMによるFIFOバッファに格納します。 SRAMはNEC uPD431016A-20で、64K×16bitの1Mbitタイプです。 約0.37秒のデータしか格納できませんが、CD-ROMドライブと本基板上のオシレータの周波数の差異が小さければ、アンダーフローやオーバーフローは実用上問題なくなると期待できます。 SRAMのアドレス制御とCS/WE/OE、HC595の出力制御と次段のHCT574のラッチタイミングは、1チップマイコンのAVR AT90S8515で生成しています。

SRAMに格納されたデータは、1チップマイコンからのタイミング制御を受けてHCT574でラッチします。 SRAMが5VTTL出力なので、HCT素子を使用しています。

HCT574の出力は、HC166でシリアル変換して出力します。

クロックは、11.2896MHzのオシレータの出力をHC393で分周して32fsクロックと44.1kHzクロックを生成します。 それらをHC541を通して分配します。

AT90S8515用のセラロックは、回路図では8MHzですが、実機では10MHzで使用しています。 たまたま手持ち部品が10MHz品だっただけですが、8MHzでの実機確認は行っていません。

DAIからのLRCKの立ち上がりと立ち下がりでSRAMにデータを格納し、基板上のオシレータから生成したLRCKの立ち上がりと立ち下がりで読み出します。 入力データはHC595でラッチされており、SRAMから読み出したデータも次段のHCT574でラッチするため、タイミングはかなり余裕が有り、格納と読み出しが競合しても問題にはなりません。

プログラムとライタ用書き込みファイル (ver 1.0)。

SRAMのFIFOバッファーメモリが溢れた時 (オーバーフロー)と枯渇した時(アンダーフロー)には、それぞれLEDを約1秒点灯させます。 ただし、制御が甘いためか逆のLEDが点灯することが有ります。

秋月のEタイプのユニバーサル基板を使用しました。 電源は78L005で5Vを生成するため、入力は8V以上が必要です。 また、出力部のオシレータ、HC393、HC541、HC14とそれ以外で78L005を別にしています。

オシレータは、CITIZENの100ppm品を使用しています。Digi-Keyで購入しました。 SOJタイプなので、8pinのICソケットにハンダ付けして、別のオシレータと交換できるようにしています。

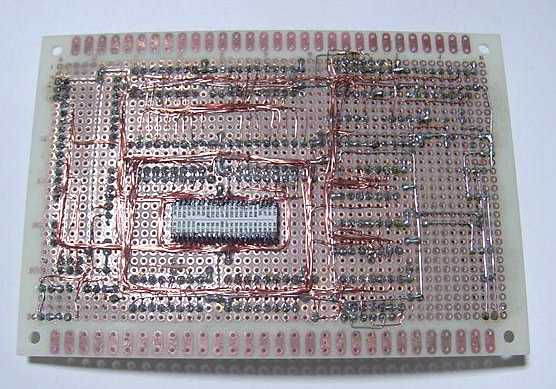

SRAMはSOJなので、基板裏面に両面テープで貼付けています。 また、ピン数が44pinと多くピッチも狭いので、配線間違いをしないようにピン番号とピン名称を記した紙をプリンタで作成し、貼付けています。

以下の機器を接続して動作確認をしました。

入力

出力

CR-583Jを入力にすると、5分程度でオーバーランが発生してしまいます。 CR-583Jに搭載されたオシレータの精度が悪いのでしょうか...

本回路を通した場合と通さない場合の音質の違いは、私の耳では分かりません... 今回使用したオシレータの品質が悪いのか、そもそも今回問題にしたジッタは音質には関係ないのか、もう少し研究が必要のようです。